# LogiCORE DDS v1.0 IP 用户手册

上海安路信息科技股份有限公司

UG117 (v. 1.0) 2021 年 11 月

Confidential

## 目 录

|                           |           |

|---------------------------|-----------|

| <b>目 录</b> .....          | <b>I</b>  |

| <b>1 产品规格</b> .....       | <b>1</b>  |

| 1.1 简介 .....              | 1         |

| 1.2 特点.....               | 错误!未定义书签。 |

| 1.3 应用 .....              | 1         |

| <b>2 工作原理</b> .....       | <b>2</b>  |

| 2.1 输出频率及频率分辨率 .....      | 2         |

| 2.2 相位增量 .....            | 3         |

| <b>3 频谱杂散分析及优化</b> .....  | <b>4</b>  |

| 3.1 频谱杂散分析 .....          | 4         |

| 3.2 频谱杂散优化 .....          | 7         |

| <b>4 IP 架构及功能介绍</b> ..... | <b>10</b> |

| 4.1 DDS 架构 .....          | 10        |

| 4.2 功能介绍 .....            | 11        |

| 4.2.1 硬件参数 .....          | 11        |

| 4.2.2 波形/相位输出 .....       | 12        |

| 4.2.3 相位抖动 .....          | 12        |

| 4.2.4 频率/相位调制 .....       | 12        |

| 4.2.5 查找表压缩 .....         | 13        |

| 4.2.6 端口信号可选 .....        | 13        |

| 4.2.7 复位电平可选 .....        | 14        |

| <b>5 IP 使用</b> .....      | <b>15</b> |

---

|                    |           |

|--------------------|-----------|

| 5.1 接口时序.....      | 15        |

| 5.2 配置参数.....      | 17        |

| 5.3 资源消耗及性能表现..... | 19        |

| <b>6 版本信息.....</b> | <b>23</b> |

| 免责声明.....          | 23        |

## 1 产品规格

### 1.1 简介

DDS（直接数字合成器）是一款逻辑 IP 核，它可以提供适用于多种场景的正弦/余弦波形。DDS 主要由相位发生器和正弦/余弦查找表组成。

直接数字合成器也叫做 NCO (Numerically Controlled Oscillator) 数控振荡器，是一种数字频率合成技术，通过设置频率字和相位字，基本可以合成任意的频率。DDS 技术能够对输出信号的频率、相位及幅度进行精确和快速地控制，且基于定点计算，易于在数字电路中实现，具有成本低，精度高，转换速度快等优点。广泛应用于频率综合、信号调制与解调、任意波形信号生成、专用 IC 设计等领域。

### 1.2 特性

- 适用于上海安路信息科技股份有限公司的全系列 **FPGA** 产品

- 用户可以选择复位方式（高电平复位/低电平复位）

- 用户可以选择正弦/余弦、单端口/双端口信号输出

- 用户可以选择是否添加相位抖动电路并且可以配置相位抖动的位宽

- 具有高精度的输出信号频率分辨率，最高可以配置 54 bit 的相位累加器

- 3~16 bit 的相位角位宽

- 3~26 bit 的输出信号数据位宽，以二进制补码的形式输出

- 可以产生固定频率信号，也可以产生频率调制/相位调制信号

- 用户可以选择是否需要系统时钟使能、同步清除、输出数据有效标志、相位输出等端口

- 用户可以选择是否需要添加 **ROM** 输出缓存

### 1.3 应用

- 数字收音机及调制解调器

- 软件定义无线电（**SDR**）

- 数字上/下转换器蜂窝及 **PCS** 基站

- 数字锁相环路中的波形合成

- 产生模拟混频器的输入信号

## 2 工作原理

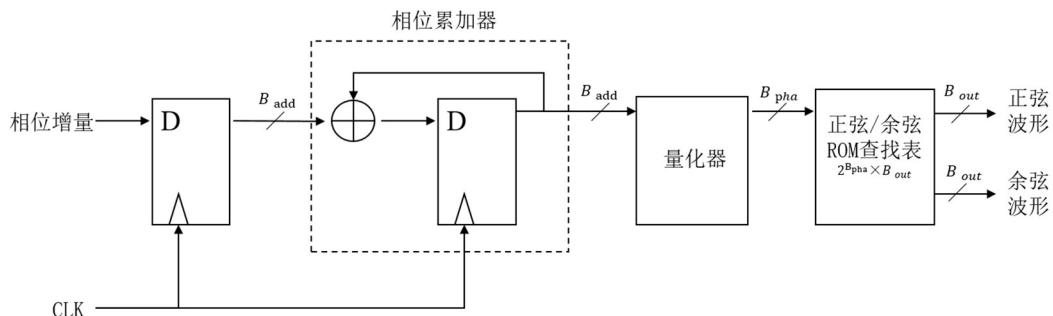

典型的 DDS 架构是由相位累加器和正弦/余弦查找表组成的，如图 2-1 所示：

图 2-1 DDS 基本原理

首先由相位累加器计算相位，然后采用量化器对相位进行截断，将累加器输出相位转化为较低精度的相位角，该相位角作为查找表的输入地址，查找表从相位到幅值进行映射，最后形成相应频率的正弦/余弦数字信号输出。DDS 采用相位寻址并结合正/余弦查找表形成了一个任意频率的正弦采样。若需要获得模拟波形，则可以将 DDS 输出的数据样本输入模数转换器（DAC）及低通滤波器，以获得具有特定频率结构的模拟波形。

### 2.1 输出频率及频率分辨率

DDS 输出波形的频率是与系统时钟频率( $f_{sys}$ )、相位累加器位宽( $B_{add}$ )、相位增量( $\Delta_\theta$ )相关的函数，可表示为：

$$f_{out} = \frac{f_{sys} * \Delta_\theta}{2^{B_{add}}}$$

在输出固定频率的模式下，DDS IP 会根据用户设置的输出频率 $f_{out}$ 计算出对应的相位增量 $\Delta_\theta$ ，在频率调制模式下，用户通过频率字端口输入相位增量，从而控制 DDS 输出波形的频率。

例如，若 DDS 的参数为：

$$f_{sys} = 100MHz$$

$$B_{add} = 12$$

$$\Delta_\theta = 50$$

可以计算出 DDS 的输出频率为：

$$f_{out} = \frac{f_{sys} * \Delta_\theta}{2^{B_{add}}}$$

$$= \frac{100 * 10^6 * 50}{2^{12}} \\ = 1.2207 \text{MHz}$$

DDS 输出波形的频率分辨率是与系统时钟频率( $f_{sys}$ )及相位累加器位宽( $B_{add}$ )相关的函数，可表示为：

$$\Delta_f = \frac{f_{sys}}{2^{B_{add}}}$$

例如，若 DDS 的参数为：

$$f_{sys} = 100 \text{MHz}$$

$$B_{add} = 32$$

则 DDS 的频率分辨率为：

$$\Delta_f = \frac{f_{sys}}{2^{B_{add}}}$$

$$= \frac{100 * 10^6}{2^{32}}$$

$$= 0.023283 \text{Hz}$$

## 2.2 相位增量

相位增量是无符号数，因此相位增量是用 0 进行扩展，而不是采用符号位进行扩展。当相位增量的位宽与相位累加器的位宽( $B_{add}$ )一致时，它无论被认为是有无符号数都没有影响。范围  $0 \sim 2^{B_{add}}$  描述的是相位  $0 \sim 2\pi$ ，而范围  $-2^{B_{add}-1} \sim 2^{B_{add}-1}$  描述的是相位  $-\pi \sim \pi$ 。相位增量决定了 DDS 的输出频率，假设 DDS 的硬件参数如下：

$$f_{sys} = 100 \text{MHz}$$

$$B_{add} = 18$$

例如产生 24MHz 频率的正弦信号，所需要的相位增量为：

$$\Delta_\theta = \frac{f_{out} * 2^{B_{add}}}{f_{sys}} \\ = \frac{24 * 10^6 * 2^{18}}{100 * 10^6} \\ = 62914.56$$

但是 DDS 内部的相位增量必须被截断为一个整数，因此实际的输出频率可以表示为：

$$f_{out} = \frac{f_{sys} * \Delta_\theta}{2^{B_{add}}}$$

$$= \frac{62914 * 100 * 10^6}{2^{18}}$$

$$= 23.999786 \text{ MHz}$$

## 3 频谱杂散分析及优化

### 3.1 频谱杂散分析

通过查找表映射的正弦/余弦信号保真度受到量化过程中相位和幅值的精度影响。查找表的深度和宽度分别影响信号的相位角分辨率及幅值分辨率，它们带来的影响相当于信号的时基抖动和幅值量化，会给 DDS 输出信号的频谱带来杂散及白色底噪声。

相位累加器的位宽和系统时钟频率共同决定了 DDS 的频率分辨率，因此相位累加器需要有足够的位宽来达到所需的频率分辨率。在大多数实际应用中，相位累加器需要分配较高的位宽以满足系统的频率分辨率。例如，若所需的频率分辨率  $\Delta_f = 1 \text{ Hz}$ ，系统时钟频率  $f_{sys} = 120 \text{ MHz}$ ，则相位累加器所需要的位宽可以表示为：

$$B_{add} = \left\lceil \log_2 \left( \frac{f_{sys}}{\Delta_f} \right) \right\rceil$$

$$= \left\lceil \log_2 \left( \frac{120 * 10^6}{1} \right) \right\rceil$$

$$= [26.8385]$$

$$= 27 \text{ bits}$$

上式中  $\lceil \rceil$  为上限操作符。由于内存需求过大，相位累加器的全精度不能用于索引正弦/余弦查找表，因此相位角会被截断，也就造成相位角精度的量化，因此会在输出波形中引入时基抖动，这种抖动也可以解释为是一种与抖动误差成正比的相位调制，假设理想的相位为  $\theta_i$ ，量化后的相位为  $\theta_q$ ，则可以推断出下式：

$$\theta_i = \theta_q + \delta_\theta$$

$$e^{j\theta_i} = e^{j(\theta_q + \delta_\theta)} = e^{j\theta_q} e^{j\delta_\theta}$$

$$\approx e^{j\theta_q} (1 + j\delta_\theta)$$

$$= e^{j\theta_q} + j\delta_\theta e^{j\theta_q}$$

下面对 DDS 模型进行仿真，分析 DDS 的频谱性能：

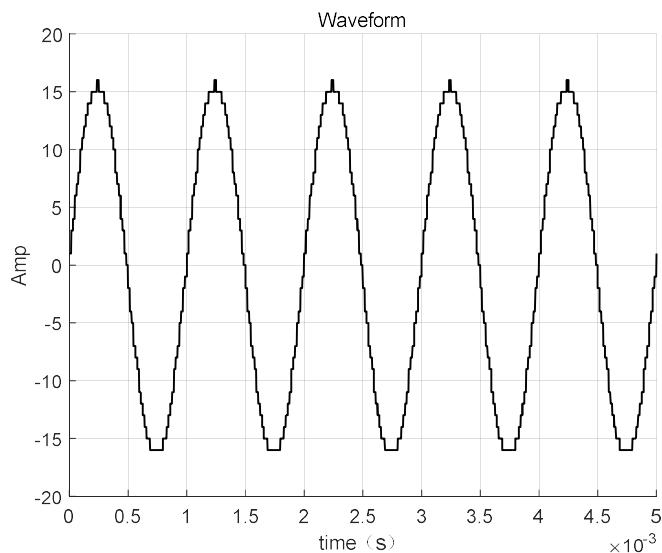

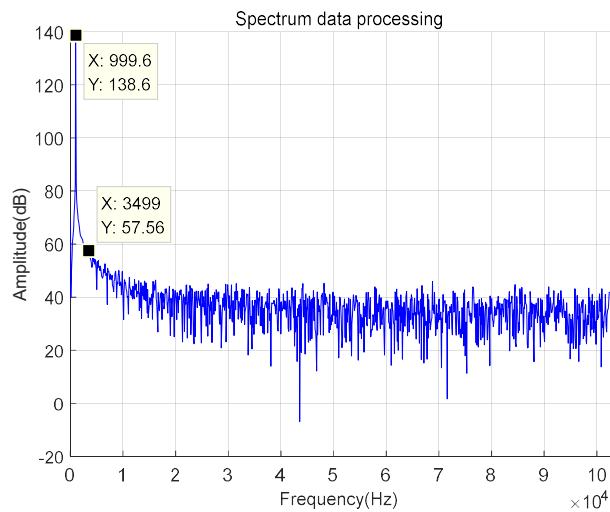

1) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 6bit、输出数据宽度为 6bit 时, DDS 输出信号及频谱分别如图 3-1、3-2 所示, SFDR (无杂散动态范围) 为 42.4dB。

图 3-1 DDS 输出信号 (W\_PHASE=32、W\_PHASE\_ANGLE=6、W\_DOUT=5)

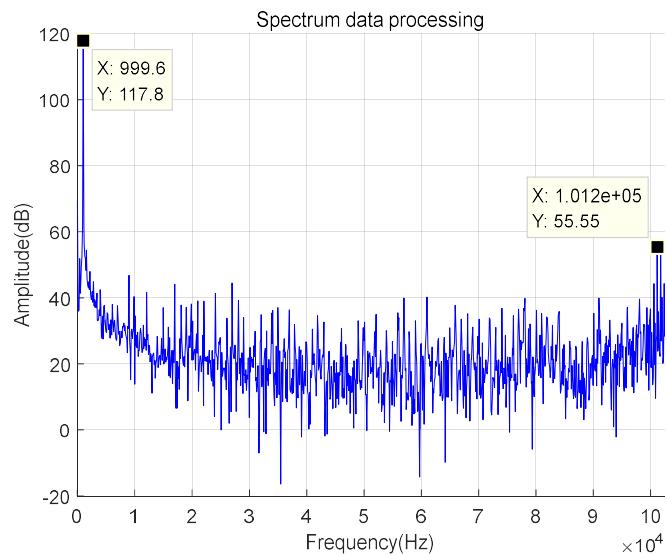

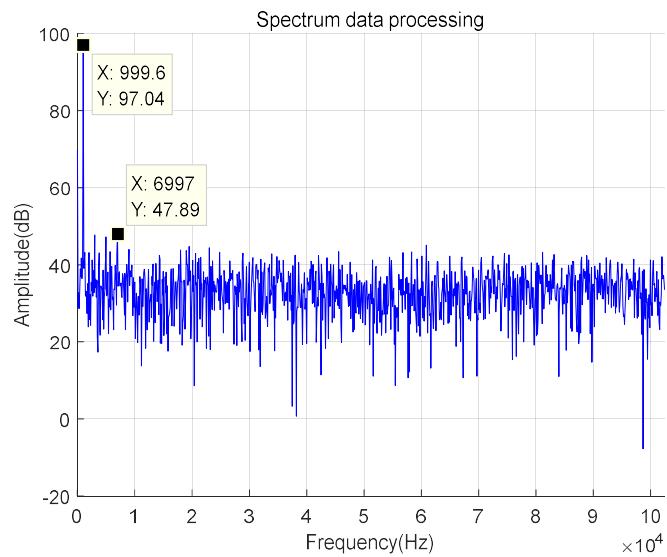

图 3-2 DDS 输出信号频谱 (W\_PHASE=32、W\_PHASE\_ANGLE=6、W\_DOUT=5)

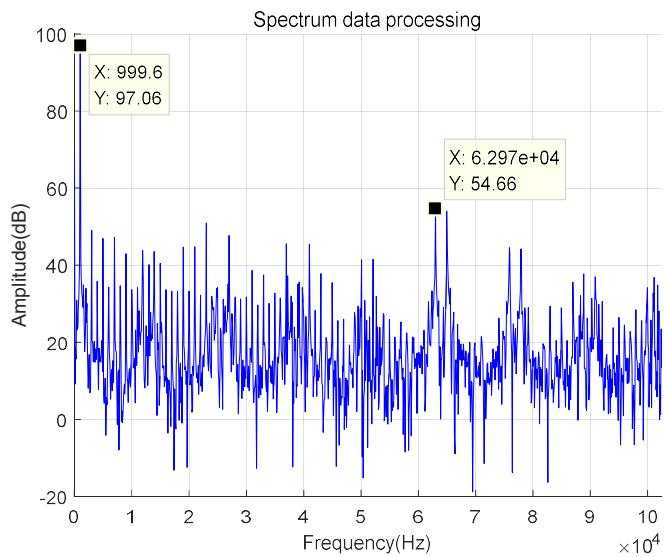

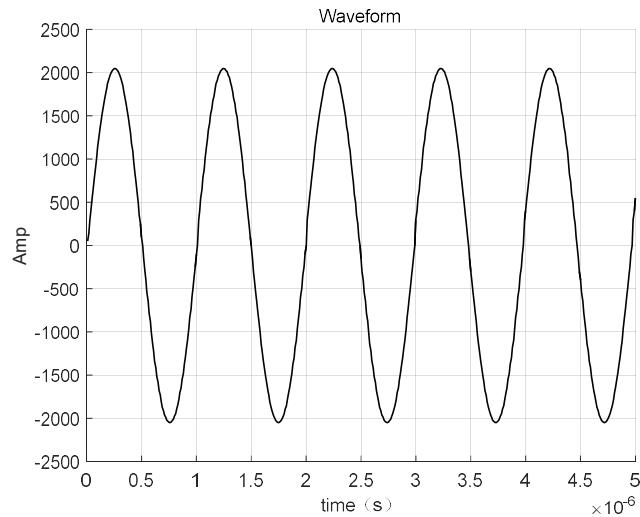

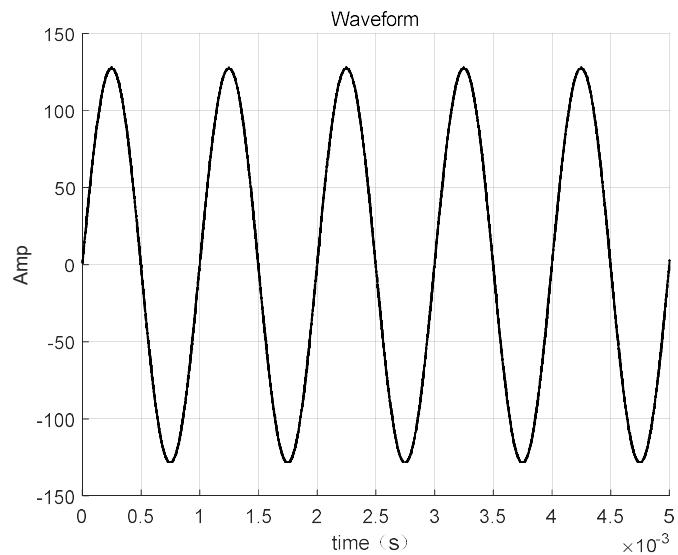

2) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 9bit、输出数据宽度为 9bit 时, DDS 输出信号及频谱分别如图 3-3、3-4 所示, SFDR (无杂散动态范围) 为 62.25dB。

图 3-3 DDS 输出信号 (W\_PHASE=32、W\_PHASE\_ANGLE=9、W\_DOUT=8)

图 3-4 DDS 输出信号频谱 (W\_PHASE=32、W\_PHASE\_ANGLE=9、W\_DOUT=8)

3) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 12bit、输出数据宽度为 11bit 时, DDS 输出信号及频谱分别如图 3-5、3-6 所示, SFDR (无杂散动态范围) 为 76.83dB。

图 3-5 DDS 输出信号 ( $W\_PHASE=32$ 、 $W\_PHASE\_ANGLE=12$ 、 $W\_DOUT=11$ )

图 3-6 DDS 输出信号频谱 ( $W\_PHASE=32$ 、 $W\_PHASE\_ANGLE=12$ 、 $W\_DOUT=11$ )

## 3.2 频谱杂散优化

在图 1 中所示的 DDS 结构当中，量化器通过舍弃高精度相位累加器中的低位部分，在相位角中引入了相位误差，舍弃的部分是一个周期的序列，这将会在频谱中产生较大的杂散。可以通过添加随机噪声来打破相位误差的规律，从而抑制信号的杂散情况。

这个随机的序列，可以称之为相位抖动的添加，其方差近似等于相位累加器的最小有效整数位。将抖动序列添加到相位累加器的输出中，然后再进行相位的量化。下面对添加相位抖动的 DDS 进行仿真，分析 DDS 的频谱性能：

- 1) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 6bit、输出数据宽度为 6bit 时，DDS 输出信号及频谱分别如图 3-7、3-8 所示，SFDR（无杂散动态范围）为 49.15dB。

图 3-7 DDS 输出信号 (W\_PHASE=32、W\_PHASE\_ANGLE=6、W\_DOUT=5)

图 3-8 DDS 输出信号频谱 (W\_PHASE=32、W\_PHASE\_ANGLE=6、W\_DOUT=5)

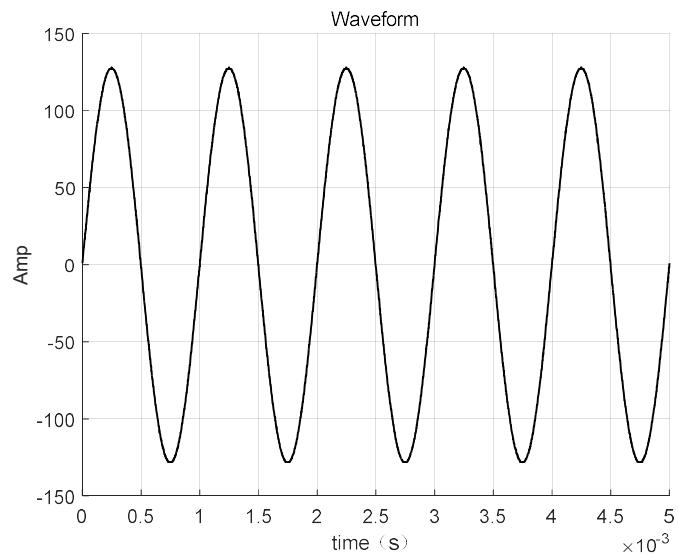

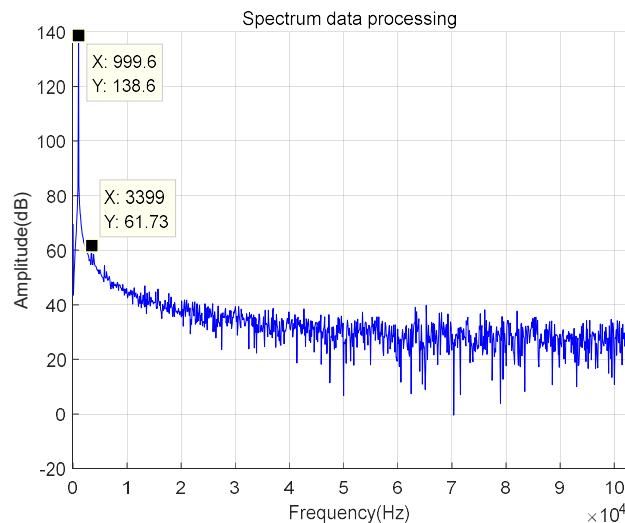

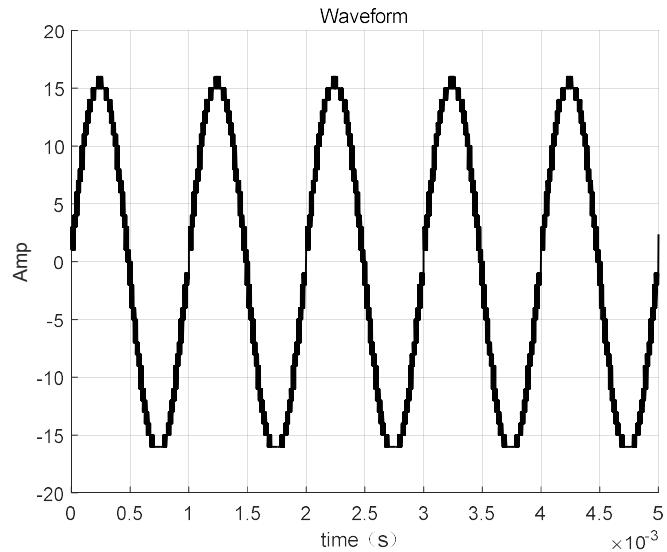

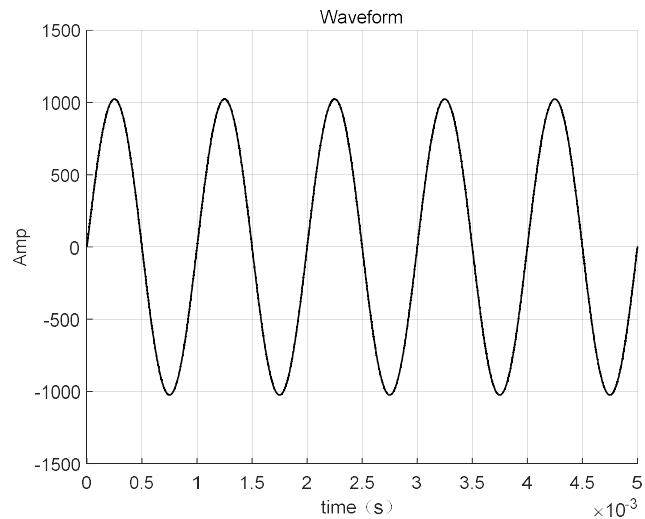

2) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 9bit、输出数据宽度为 9bit 时, DDS 输出信号及频谱分别如图 3-9、3-10 所示, SFDR (无杂散动态范围) 为 70.5dB。

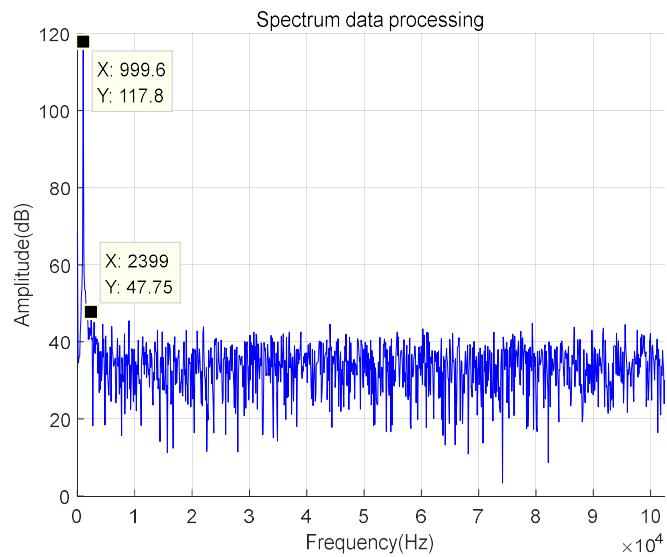

图 3-9 DDS 输出信号 (W\_PHASE=32、W\_PHASE\_ANGLE=9、W\_DOUT=8)

图 3-10 DDS 输出信号频谱 (W\_PHASE=32、W\_PHASE\_ANGLE=9、W\_DOUT=8)

3) DDS 系统时钟频率为 100MHz、输出频率为 1KHz、相位累加器宽度为 32bit、相位角宽度为 12bit、输出数据宽度为 11bit 时, DDS 输出信号及频谱分别如图 3-11、3-12 所示, SFDR (无杂散动态范围) 为 81.04dB。

图 3-11 DDS 输出信号 ( $W\_PHASE=32$ 、 $W\_PHASE\_ANGLE=12$ 、 $W\_DOUT=11$ )

图 3-12 DDS 输出信号频谱 ( $W\_PHASE=32$ 、 $W\_PHASE\_ANGLE=12$ 、 $W\_DOUT=11$ )

从仿真的结果可以看出，相位抖动的添加在一定程度上可以优化 DDS 输出信号的频谱，可以抑制相位截断带来的信号杂散，增加 DDS 输出信号的 SFDR (大约 6dB)。

## 4 IP 架构及功能介绍

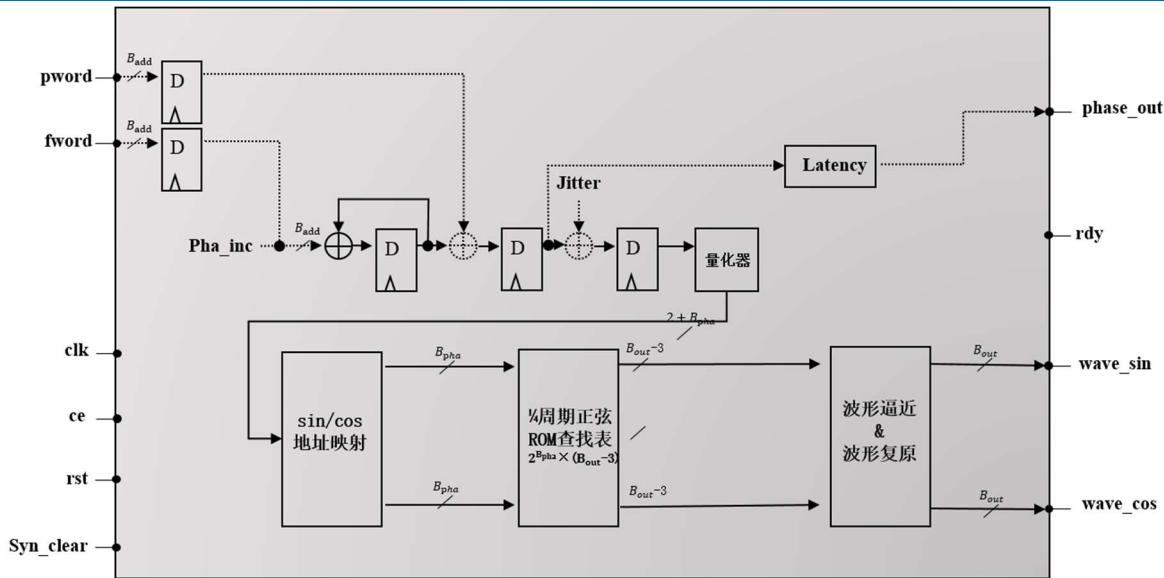

### 4.1 DDS 架构

图 4-1 DDS IP 核架构

DDS IP 核的架构如图 4-1 所示，DDS IP 核主要由相位累加器及正弦查找表构成，通过相位量化、地址映射、波形残差值查找以及波形逼近及复原，最终输出频率可控的正弦/余弦信号。用户可以配置 DDS 产生正弦或余弦波形，也可以配置 DDS 同时输出正弦信号和余弦信号（双端口输出），还可以选择是否输出波形相位；用户可以选择配置 DDS 输出单一频率的信号，也可以配置 DDS 产生调频信号。

## 4.2 功能介绍

### 4.2.1 硬件参数

DDS 的硬件参数包括相位累加器位宽 **W\_PHASE**、输出波形位宽 **W\_DOUT**、相位角位宽 **W\_PHASE\_ANGLE**。

其中，**W\_PHASE** 主要影响 DDS 输出信号的频率分辨率  $\Delta f$ ，可用下式表示：

$$\Delta f = \frac{f_{clk}}{2^{W\_PHASE}}$$

上式中  $f_{clk}$  表示系统时钟频率。

**W\_PHASE\_ANGLE** 及 **W\_DOUT** 影响 DDS 输出信号的频谱无杂散动态范围 (SFDR) 及信噪比 (SNR)，可用经验公式表示：

$$SFDR = -(6.02*W\_PHASE\_ANGLE - 3.992)$$

$$SNR = -(6.02*W\_DOUT + 1.76)$$

DDS IP 采用参数化设计，用户可以根据应用场景对 **W\_PHASE**、**W\_DOUT**、**W\_PHASE\_ANGLE** 进行配置。其中，**W\_PHASE** 可配置范围为 3~54bit，**W\_DOUT** 的可配置范围为 3~26bit，**W\_PHASE\_ANGLE** 的可配置范围为 3~16bit，当 **W\_PHASE** 设置值小于 **W\_DOUT** 时，**W\_PHASE** 所设参数无效，**W\_PHASE** 将会取与 **W\_DOUT**

相等的参数值。

### 4.2.2 波形/相位输出

DDS v1.0 支持正弦/余弦 (sin/cos) 波形输出以及相位 (phase) 输出。

用户可以选择单端口波形输出或双端口波形输出, DDS 波形是通过查找表进行输出的, 如图 2-1 所示相位经过量化后作为查找表的输入地址, 读取对应的波形数据并输出。**sin** 输出与 **cos** 输出共用同一查找表, 而寻址的方式有所不同, 如图 4-1 所示, 这样做可以有效节省系统的资源。

用户可以选择是/否输出 DDS 相位, DDS 相位是通过对量化前的累加相位进行延时, 与 DDS 波形同步输出, 如图 2 所示。

### 4.2.3 相位抖动

DDS v1.0 为用户提供了相位抖动功能选项, 用户可以通过配置抖动噪声的位宽决定相位抖动的幅度。

由于相位量化过程中累加器输出的相位会被截断, 舍去了部分的低位数据, 因此在相位斜率中引入了相位误差。由于相位的小数部分被丢弃, 相位误差将会是一个周期的序列, 这将会降低 DDS 输出信号的 SFDR。

相位抖动功能是通过在量化前的相位中添加随机序列, 使得量化后的相位误差不再呈明显的周期变化, 可以降低 DDS 输出信号频谱中的杂散噪声, 提高 DDS 输出信号的 SFDR。

为了使随机序列的周期尽可能长, 采用 **m** 序列作为 DDS 的相位抖动输入。**m** 序列是最长线性反馈移位寄存器序列的简称。它是由带线性反馈的移存器产生的周期最长的序列。一般来说, 一个 **n** 级线性反馈移存器可能产生的最长周期等于  $(2^n - 1)$ 。

### 4.2.4 频率/相位调制

DDS v1.0 为用户提供了频率调制功能、相位调制功能选项。

在频率调制模式下, 用户可以通过频率字输入端口 (**fword**) 对 DDS 输出信号进行频率调制, **fword** 位宽与 **W\_PHASE** 一致, DDS 输出信号频率  $f_{out}$  可表示为:

$$f_{out} = \frac{f_{clk} * \text{fword}}{2^{\text{W\_PHASE}}}$$

在相位调制模式下, 用户可以通过相位字输入端口 (**pword**) 对 DDS 输出信号的相位进行调制, **pword** 位宽与 **W\_PHASE** 一致, DDS 的输出信号的相位  $phase_{out}$  可表示为:

$$phase_{out} = \frac{pword}{2^{\text{W\_PHASE}}} * 2\pi + phase_{dds}$$

上式中： $phase_{dds}$  表示相位调制前输出信号的相位。

#### 4.2.5 查找表压缩

DDS 输出信号的无杂散动态范围 (SFDR) 及信噪比 (SNR) 主要与查找表的深度与宽度有关，因此要提升 DDS 输出信号的质量，需要消耗大量的 ROM 资源或 Block RAM 资源。通过对查找表波形压缩的方式优化 DDS 的资源，在消耗资源不变的情况下可以储存更多的波形数据，从而提升 DDS 的性能。

DDS v1.0 采用查找表对称压缩&波形逼近，可以有效将查找表的深度减少为压缩前的四分之一，将查找表的数据位宽减少 3bit。

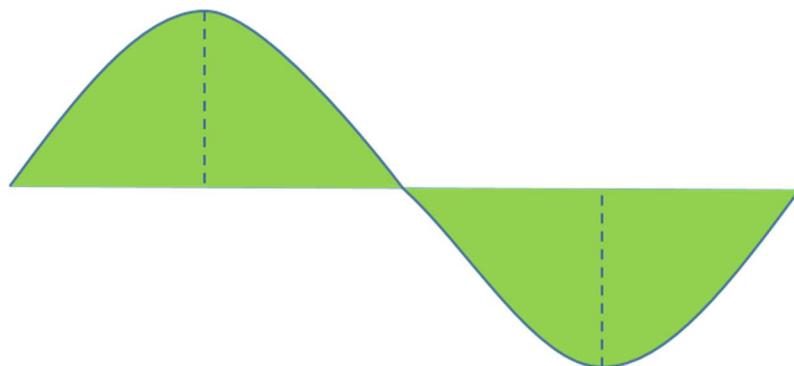

图 4-2 对称压缩

如图 4-2 所示，利用正弦/余弦函数的对称性，只需要储存正弦函数四分之一周期的波形即可，通过截断后的相位角中的两个有效位即可对不同的象限函数的波形进行寻址，进而还原整个正弦/余弦函数，该方法可以将查找表的深度减少为压缩前的四分之一，将查找表的数据位宽减少 1bit。

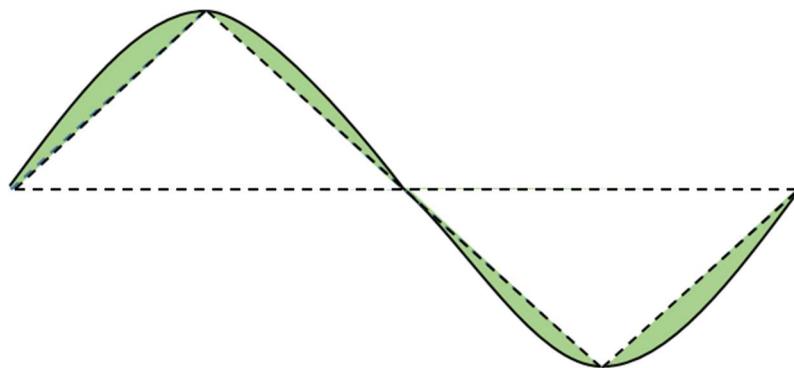

图 4-3 波形逼近

如图 4-3 所示，用三角波函数来逼近正弦函数，在该方法中三角波函数可以用 ROM/RAM 的地址信号间接表示，查找表中只需要储存三角波函数与正弦函数的残差即可。在对称压缩的基础上将查找表的数据宽度减少 2bit。

#### 4.2.6 端口信号可选

DDS v1.0 为客户提供若干端口信号可选功能，可选的端口包括：**ce**（时钟有效）、**syn\_clear**（同步清除）、**rdy**（输出有效）。

当用户选择 **ce** 端口有效时，**ce** 就会作为 DDS IP 的输入信号，当 **ce** 为高电平时，DDS IP 的输入时钟有效，反之无效。

当用户选择 **syn\_clear** 端口有效时，**syn\_clear** 就会作为 DDS IP 的输入信号，当 **syn\_clear** 拉高时，DDS IP 内部的寄存器就会进行同步清零。

当用户选择 **rdy** 端口有效时，**rdy** 就会作为 DDS IP 的输出信号，当 **rdy** 为高电平时，表示 DDS IP 的输出数据有效。

#### 4.2.7 复位电平可选

DDS v1.0 为客户提供复位电平可选功能，用户可以根据系统设计以及器件特性选择使用高电平复位或低电平复位，而且 DDS IP 的寄存器基本上是采用异步复位，同步释放的方式进行设计的。

## 5 IP 使用

### 5.1 接口时序

DDS IP 的接口如表 5-1 所示。

表 5-1 DDS IP 接口描述

| 接口        | 方向     | 描述              |

|-----------|--------|-----------------|

| clk       | input  | 时钟信号            |

| rst       | input  | 复位信号, 高电平复位     |

| ce        | input  | 输入时钟有效信号, 高电平有效 |

| Syn_clear | input  | 同步清除信号, 高电平有效   |

| fword     | input  | 频率字             |

| pword     | input  | 相位字             |

| rdy       | output | 输出有效标志信号, 高电平有效 |

| wave_sin  | output | 正弦波形输出          |

| wave_cos  | output | 余弦波形输出          |

| phase_out | output | 相位输出            |

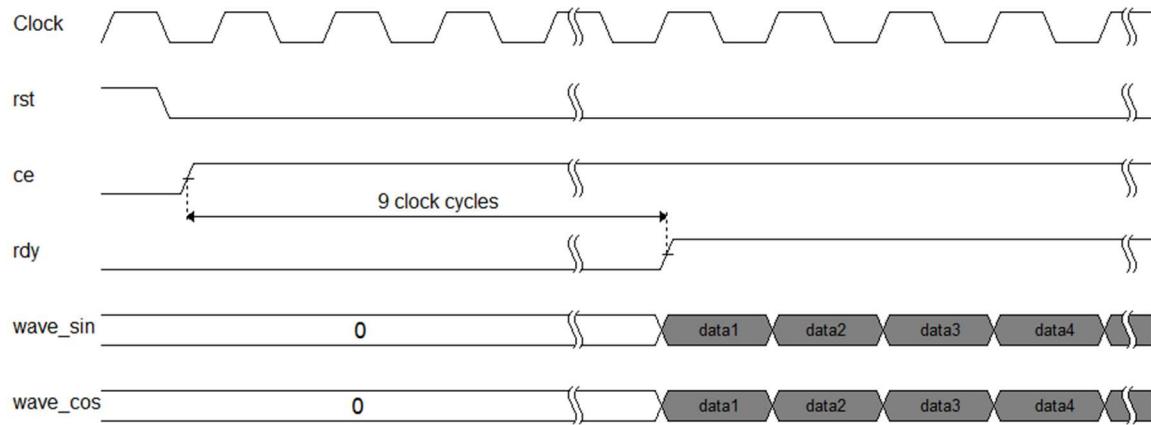

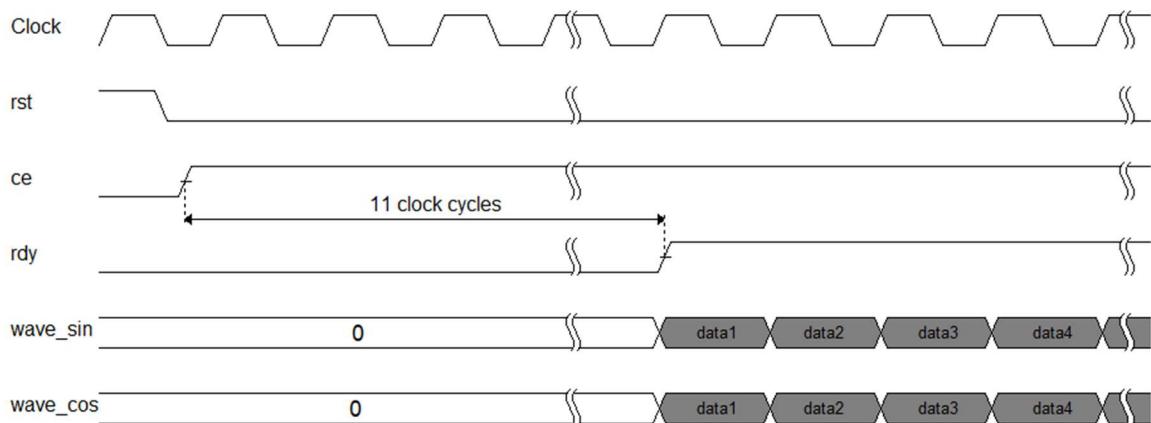

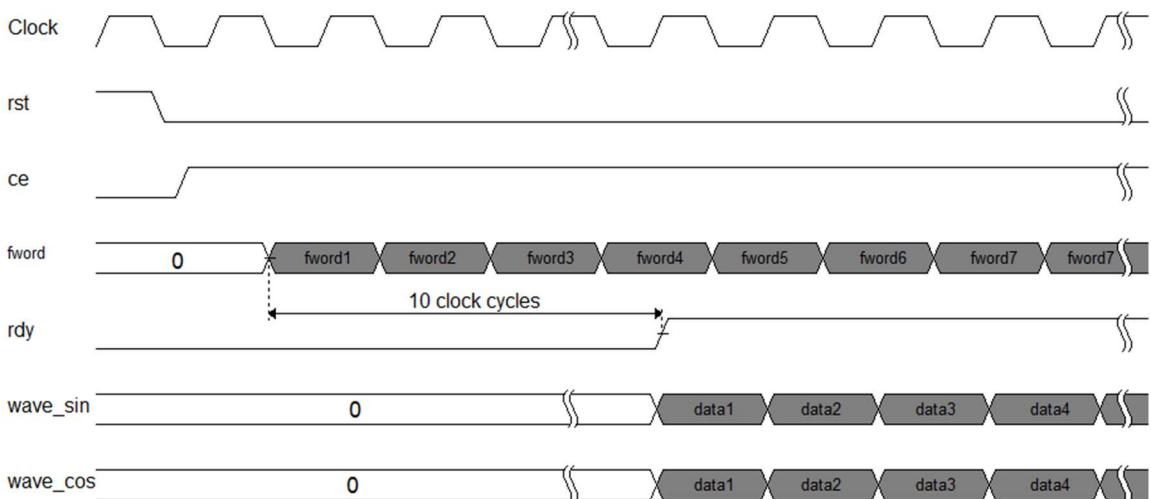

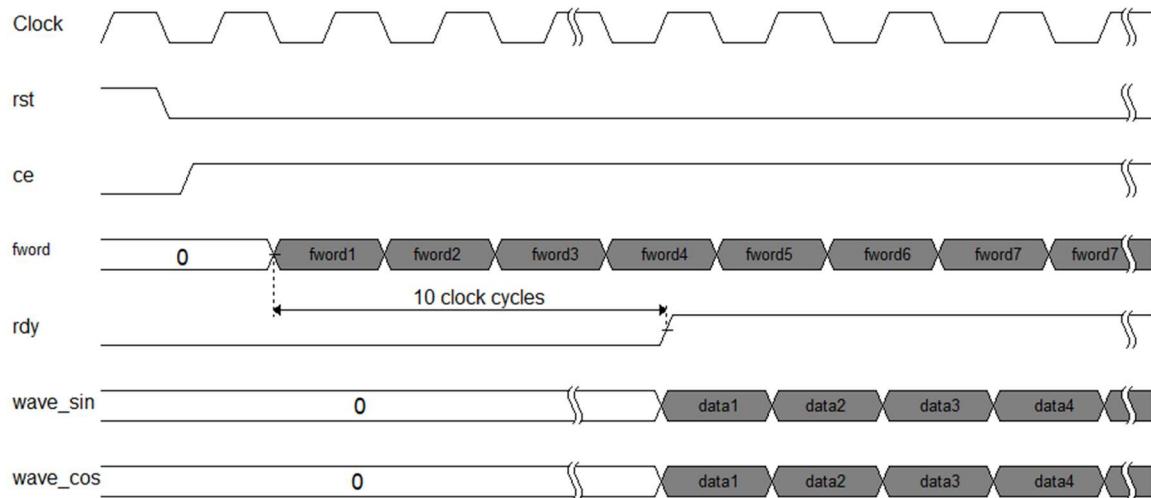

如图 5-1~图 5.4 所示, 对 DDS IP 的时序关系进行描述。图 5-1 为 DDS IP 在固定输出频率模式下的信号时序关系, 从图中可以看出当时钟输入有效后, 有效的输出数据将延迟 9 个系统时钟周期。图 5-2 为 DDS IP 在固定输出频率模式并使用 LATENCY\_ROM 功能时的信号时序关系, 从图中可以看出当时钟输入有效后, 有效的输出数据将延迟 11 个系统时钟周期。图 5-3 为 DDS IP 在调制模式下的信号时序关系, 从图中可以看出当时钟输入有效后, 有效的输出数据将延迟 10 个系统时钟周期。图 5-4 为 DDS IP 在调制模式并使用 LATENCY\_ROM 功能时的信号时序关系, 从图中可以看出当时钟输入有效后, 有效的输出数据将延迟 12 个系统时钟周期。

图 5-1 非频率调制下的接口时序

图 5-2 非频率调制下的接口时序 (LATENCY\_ROM)

图 5-3 频率调制下的接口时序

图 5-4 频率调制下的接口时序 (LATENCY\_ROM)

## 5.2 配置参数

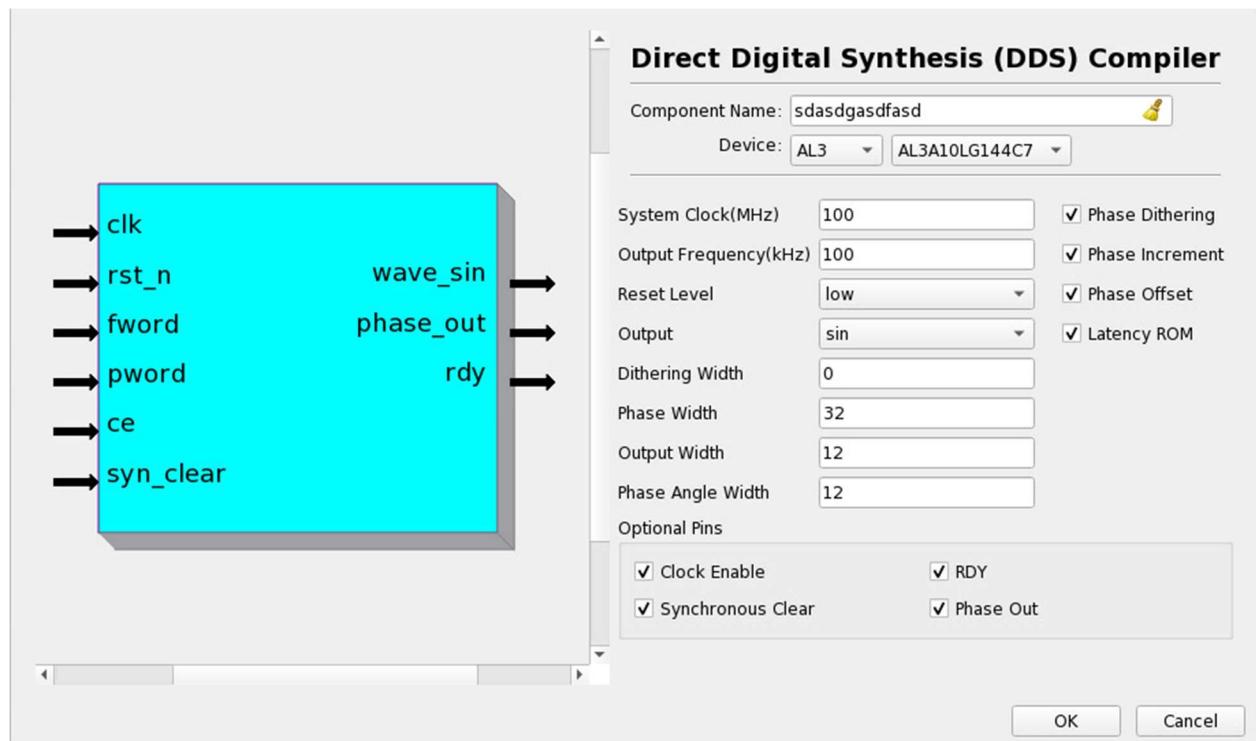

图 5-5 IP GEN 界面示意图

配置参数说明：

- System clock:

- DDS 的系统时钟频率  $f_{sys}$

- Output frequency:

- DDS 的输出信号频率  $f_{out}$

- $0 < f_{out} < f_{sys}/2$

- Reset level:

- 包含两个参数 (low/high)

- 用户可以配置 DDS IP 采用低电平复位 (low) 或高电平复位 (high)

- Output:

- 包含三个参数 (sin/cos/sin+cos)

- 用户可以选择 sin 波形输出、cos 波形输出或 sin+cos (双端口) 波形输出

- Phase Dithering:

- 两个参数 (yes/no)

- 用户可以选择是否添加相位抖动

- Dithering Width:

- 相位抖动位宽 (1~Phase Width)

- Phase Width:

- 相位累加器位宽

- 范围: 3~54 (bit)

- Output Width:

- 输出信号位宽

- 范围: 3~26 (bit)

- Phase angle Width:

- 相位角精度位宽

- 范围: 3~16 (bit)

- Phase Increment Programmability:

- 相位增量可编程性

- 两个参数 (yes/no)

- Phase Offset Programmability:

- 相位偏移量可编程性

- 两个参数 (yes/no)

- Latency ROM:

- ROM 输出缓存

- 两个参数 (yes/no)

- Clock Enable:

- 系统时钟使能信号

- 两个参数 (yes/no)

- Synchronous Clear:

- 同步清除信号

- 两个参数 (yes/no)

- RDY:

- 输出有效标志信号

- 两个参数 (yes/no)

- Phase Out:

- 相位输出

- 两个参数 (yes/no)

### 5.3 资源消耗及性能表现

表 5-2~表 5-5 为 TD5.4.31955 在不同型号器件下综合 DDS IP v1.0 所表现出来的资源消耗情况及最大系统时钟工作频率。AL3 系列器件的资源及性能表现如表 5-2 所示，所采用的器件型号为 AL3A10BG256B。

表 5-2 AL3 系列器件资源及性能

| DDS 配置       | 配置 1 | 配置 2 | 配置 3 | 配置 4 |

|--------------|------|------|------|------|

| Phase Width  | 8    | 20   | 23   | 30   |

| Output Width | 6    | 12   | 16   | 17   |

| Phase angle Width    | 6    | 10   | 12   | 15   |

|----------------------|------|------|------|------|

| Frequency Modulation | None | Yes  | None | Yes  |

| Phase Dithering      | None | None | Yes  | Yes  |

| 资源及性能表现              |      |      |      |      |

|                      | 配置 1 | 配置 1 | 配置 1 | 配置 1 |

| LUTs                 | 52   | 127  | 159  | 225  |

| REGs                 | 140  | 376  | 459  | 639  |

| BRAM                 | 1    | 1    | 2    | 8    |

| Max Frequency (MHz)  | 247  | 233  | 223  | 184  |

EF3 系列器件的资源及性能表现如表 5-3 所示，所采用的器件型号为 EF3L90CG400B。

表 5-3 EF3 系列器件资源及性能

| DDS 配置                      | 配置 1 | 配置 2 | 配置 3 | 配置 4 |

|-----------------------------|------|------|------|------|

| <b>Phase Width</b>          | 8    | 20   | 23   | 30   |

| <b>Output Width</b>         | 6    | 12   | 16   | 17   |

| <b>Phase angle Width</b>    | 6    | 10   | 12   | 15   |

| <b>Frequency Modulation</b> | None | Yes  | None | Yes  |

| <b>Phase Dithering</b>      | None | None | Yes  | Yes  |

| 资源及性能表现                     | 配置 1 | 配置 2 | 配置 3 | 配置 4 |

| <b>LUTs</b>                 | 52   | 127  | 157  | 311  |

| <b>REGs</b>                 | 140  | 376  | 459  | 643  |

| <b>BRAM</b>                 | 1    | 1    | 2    | 13   |

| <b>Max Frequency (MHz)</b>  | 232  | 207  | 187  | 161  |

EG4 系列器件的资源及性能表现如表 5-4 所示，所采用的器件型号为 EG4S20BG256。

表 5-4 EG4 系列器件资源及性能

| DDS 配置                      | 配置 1 | 配置 2 | 配置 3 | 配置 4 |

|-----------------------------|------|------|------|------|

| <b>Phase Width</b>          | 8    | 20   | 23   | 30   |

| <b>Output Width</b>         | 6    | 12   | 16   | 17   |

| <b>Phase angle Width</b>    | 6    | 10   | 12   | 15   |

| <b>Frequency Modulation</b> | None | Yes  | None | Yes  |

| <b>Phase Dithering</b>      | None | None | Yes  | Yes  |

| 资源及性能表现                     | 配置 1 | 配置 2 | 配置 3 | 配置 4 |

|                            |     |     |     |     |

|----------------------------|-----|-----|-----|-----|

| <b>LUTs</b>                | 53  | 128 | 157 | 238 |

| <b>REGs</b>                | 140 | 376 | 459 | 639 |

| <b>BRAM</b>                | 1   | 1   | 2   | 4   |

| <b>Max Frequency (MHz)</b> | 210 | 184 | 179 | 173 |

PH1 系列器件的资源及性能表现如表 5-5 所示，所采用的器件型号为 PH1A400SFG900。

表 5-5 PH1 系列器件资源及性能

| <b>DDS 配置</b>               | <b>配置 1</b> | <b>配置 2</b> | <b>配置 3</b> | <b>配置 4</b> |

|-----------------------------|-------------|-------------|-------------|-------------|

| <b>Phase Width</b>          | 8           | 20          | 23          | 30          |

| <b>Output Width</b>         | 6           | 12          | 16          | 17          |

| <b>Phase angle Width</b>    | 6           | 10          | 12          | 15          |

| <b>Frequency Modulation</b> | None        | Yes         | None        | Yes         |

| <b>Phase Dithering</b>      | None        | None        | Yes         | Yes         |

| <b>资源及性能表现</b>              | <b>配置 1</b> | <b>配置 2</b> | <b>配置 3</b> | <b>配置 4</b> |

| <b>LUTs</b>                 | 33          | 58          | 92          | 112         |

| <b>REGs</b>                 | 160         | 432         | 529         | 734         |

| <b>BRAM</b>                 | 1           | 1           | 1           | 6           |

| <b>Max Frequency (MHz)</b>  | 291         | 187         | 190         | 182         |

## 6 版本信息

| 日期         | 版本   | 修订记录    |

|------------|------|---------|

| 2021/11/xx | v1.0 | 首次发布中文版 |

**版权所有 2021 上海安路信息科技股份有限公司**

未经本公司书面许可，任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部，并不得以任何形式传播。

## 免责声明

本文档并未授予任何知识产权的许可，并未以明示或暗示，或以禁止发言或其它方式授予任何知识产权许可。除安路科技在其产品的销售条款和条件中声明的责任之外，安路科技概不承担任何法律或非法律责任。安路科技对安路科技产品的销售和/或使用不作任何明示或暗示的担保，包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等，均不作担保。安路科技对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任，安路科技保留修改文档中任何内容的权利，恕不另行通知。安路科技不承诺对这些文档进行适时的更新。